Состояние программы проверки правил проектирования печатной платы

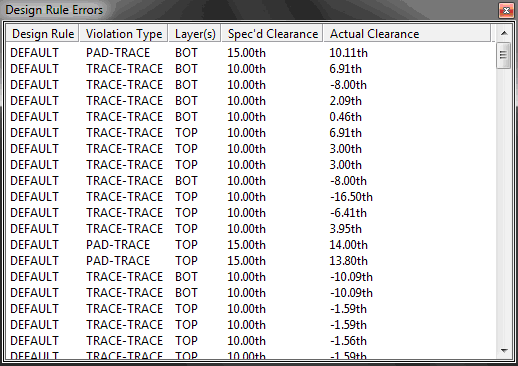

В правой нижней части окна программы находится окно программы проверки правил проектирования, работающее в режиме реального времени. Оно сообщает о любых нарушениях правил при проектировании разрабатываемой печатной платы. Щелчок левой кнопкой мыши на нем выводит диалоговое окно Design Rule Errors, выдающее подробную информацию о нарушении и позволяющее перейти к конкретной ошибке (Рис. 92). Если нажать левой кнопкой на значении в списке, то ARES выделит соответствующую метку (красная окружность), показывающую нарушение правил проектирования на печатной плате, а если дважды щелкнуть левой кнопкой на значении, то ARES выделит и изменит масштаб так, чтобы указанная метка находилась в центре экрана. На Рис. 92:

- Design Rule – название правила, которое было нарушено (DEFAULT (по умолчанию), SIGNAL (для сигнальных цепей) и т. д.);

- Violation Type – тип нарушения: PAD-TRACE (от контактной площадки к дорожке), TRACE-TRACE (от дорожки к дорожке), EDGE-PAD (от края печатной платы до контактной площадки) EDGE-TRACE (от края печатной платы до дорожки) и т. д;

- Layer(s) – слой или слои, на которых было нарушено правило (TOP – верхний медный, BOT – нижний медный, MULTIPLE – несколько слоев и т. д.);

- Spec’d Clearance – зазор, указанный в правиле с единицами измерения, например, 15.00th;

- Actual Clearance – реальный зазор на печатной плате с единицами измерения, например, 10.11th.

По щелчку правой кнопкой мыши по ошибке появляется контекстное меню, которое позволяет или проигнорировать ошибку (Ignore this error) или сделать так, чтобы игнорируемые ошибки опять учитывались при проверке (Reset Ignored Errors).